I. Frontier focus of Sino-US Integrated circuits

Recently, Professor Zhang Zhiyong-Peng Lianmao, the research group of the carbon-based electronics Research Center of Peking University and the Key Laboratory of nano-device physics and chemistry of Ministry of Education, proposed a new purification and self-assembly method for "carbon nanotubes.

High-density and high-purity semiconductor array carbon nanotube materials are prepared, and on this basis, transistors and circuits with higher performance than the silicon-based CMOS technology of the same grid length are realized for the first time, showing the advantages of carbon tube electronics.

This achievement has solved the bottleneck that has puzzled the preparation of carbon-based semiconductor materials for a long time, such as the problems of purity, density and area of materials, which has laid the foundation for carbon-based semiconductor to enter scale industrialization, it also provides great potential for China's chip manufacturing industry to realize "curve overtaking. Peng Lianmao, professor of electronics department of Peking University and academician of Chinese Academy of Sciences, said that chips made of carbon tubes are expected to be used in mobile phones and 5G micro base stations.

More widely, carbon-based technology can be applied to multiple fields such as national defense science and technology, satellite navigation, meteorological monitoring, artificial intelligence, medical devices, etc.

On May 22nd, relevant research results were published online in "Science" (volume 368, issue 6493, 850~856 pages), with "high density semiconductor carbon nanotube parallel arrays for High Performance Electronics" (Aligned, high-densitysemiconducting carbon nanotube arrays for high-performance electronics).

Liu Lijun, a 2015-level doctoral candidate in the Department of Electronics, and Han Jie, an engineer from Beijing Yuanxin carbon-based integrated circuit Research Institute, are the co-authors, and Zhang Zhiyong and Peng Lianmao are co-authors.

Following this, research from Massachusetts Institute of Technology further enlarged the commercial potential of carbon nanotubes in industrial scenarios.

On June 1st, the assistant professor of electrical engineering and computer science of Massachusetts Institute of Technology Max Shulaker team demonstrated how to batch manufacture carbon nanotube field effect transistors (CNFETs) on a 200mm standard wafer, the results were published in Fabrication of carbon nanotube field, a sub-issue of Nature, on the topic of "preparation of carbon nanotube field effect transistors in industrial silicon production equipment" (effect transistors in commercial silicon manufacturing facilities-Nature Electronics).

Integrated Carbon Nanotube Field Effect Transistor in commercial silicon foundry

Compared with traditional methods, they have improved the deposition technology based on manufacturing CNFET, speeding up the manufacturing process by more than 1100 times, and reducing the production cost at the same time. This technology deposits carbon nanotubes side to side on the wafer, and 14400 × 14400 array CFNET is distributed on multiple wafers.

At present, the team has successfully tested this new method in two different factories, including commercial silicon manufacturing plants operated by Analog Devices company and large quantities of semiconductor foundry factories operated by SkyWater Technology company.

II

The core problem of carbon-based materials was solved by Chinese team

The cornerstone of modern information technology is integrated circuit chips, and 90% of the devices that constitute integrated circuit chips are derived from silicon-based CMOS technology.

After decades of development, the integrated circuit technology based on carbon base is about to enter the technical node of 2-3nm, and the sound of Moore's law approaching the physical limit has also become the mainstream in the industry, the research on nano electronic science and technology in the post-Moor era has become increasingly urgent. The development of non-silicon-based nano electronic technology may fundamentally affect the development of chips and related industries in the future.

Among several possible silicon-based replacement technologies, carbon nanotube technology has been considered as the most likely technology to succeed by many scholars and large companies including IBM. Carbon nanotubes can be used as materials for preparing carbon-based semiconductors, which are conductive materials developed based on carbon-based nanomaterials.

However, the premise of mass preparation of carbon nanotube integrated circuits is to realize carbon nanotube array films with ultra-high semiconductor purity, CIS, high density and large area uniformity.

Compared with the previous manufacturing process, such production requirements are difficult to meet. The restriction of material problems leads to the practical performance of carbon tube transistors and integrated circuits far lower than the theoretical expectation, it has become the biggest technical challenge in the field of carbon tube electronics.

Preparing the first silicon-based CMOS device and circuit beyond similar size has always been a dream in the field of basic preparation materials.

Peng Lianmao, professor of Peking University, academician of Chinese Academy of Sciences. Since 2000, Peng Lianmao has been sticking to the field of carbon-based nano-electronics for nearly 20 years. He has led the research team to explore the method of preparing integrated circuits with carbon nano-tube materials, and has made great efforts all the way. Known as the leader of domestic carbon chip development.

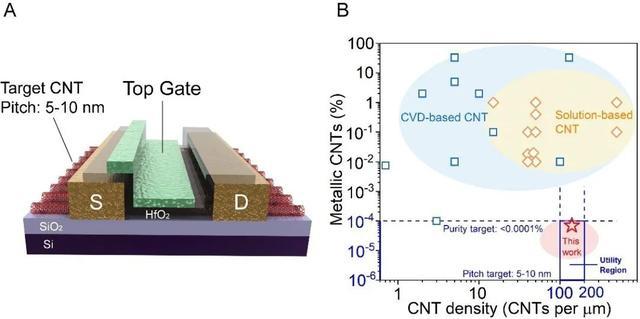

Professor Zhang Zhiyong of Peking University-Professor Peng Lianmao's research group used polymer dispersion and purification technology for many times to obtain ultra-high purity carbon tube solution, and combined with dimension limit self-arrangement method, A carbon tube array with a density of 120 /μm, a semiconductor purity of 99.9999% and a diameter distribution of 1.45±0.23 nm was prepared on a 4-inch substrate, on this basis, it is the first time to realize transistors and circuits whose performance surpasses the silicon-based CMOS technology of the same grid length, thus meeting the demand of ultra-large scale carbon tube integrated circuits.

Requirements of large-scale integrated circuits on carbon tube materials: the premise of mass preparation of carbon nanotube integrated circuits is to realize ultra-high semiconductor purity (>99.9999%), CIS, high density (100~200 /μm), large area uniform carbon nanotube array film.

Starting from the commercially available carbon nanotubes, the research group put them into the toluene solvent and added polymers into them, and then put them into the centrifuge to sort the coated nanotubes. Repeat the process twice and further sort them. As a result, 99.9999% nano-tube solution is obtained, which is improved compared with 99.99% achieved by the previous method. Researchers said that the selection rate of nanotubes can be further improved by repeating the process many times.

Preparation and characterization of high density and high purity semiconductor carbon tube arrays

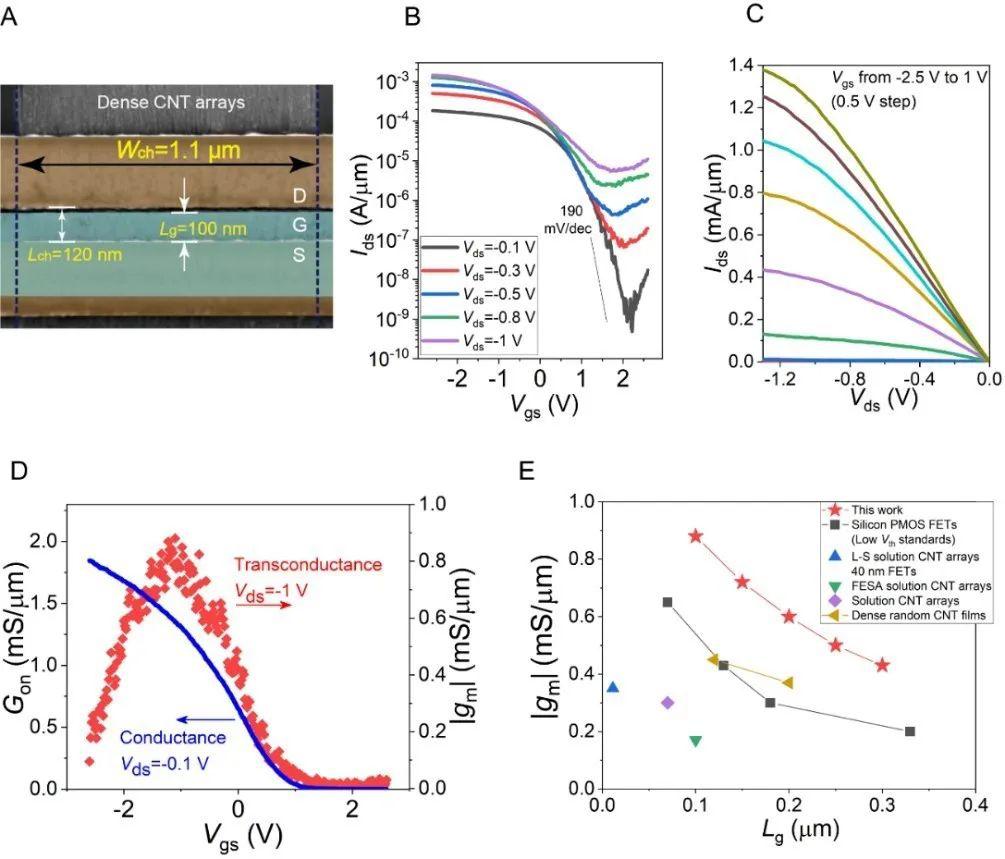

Based on this material, field effect transistors and ring oscillator circuits are prepared in batches, the peak transconductivity and saturation current of the 100nm grid-length carbon tube transistor reach 0.9mS/μm and 1.3mA/μm(VDD = 1V), respectively, the sub-threshold swing at room temperature is 90mV/DEC.

High performance carbon tube transistor

The fifth-order ring oscillator circuits have been prepared in batches, with the finished product rate exceeding 50%, the highest oscillation frequency of 8.06GHz far exceeding the published circuits based on nanomaterials, and exceeding the similar size of silicon-based CMOS devices and circuits.

Carbon tube High Speed Integrated Circuit

According to Peng Lianmao's team, carbon nanotubes, as a new type of nano-semiconductor material, have special advantages in physics, electronics, chemistry and machinery. As early as 2018, they used carbon nanotube network films as materials to prepare high-performance CMOS electronic devices on ultra-thin flexible substrates, and successfully applied the sensor integration system to human body information monitoring.

In an interview with the media, Beijing carbon-based integrated circuit research institute where Peng Lianmao and Zhang Zhiyong work said that carbon-based technology has better performance and lower power consumption than silicon-based technology, the comprehensive advantage of performance and power consumption is 5 to 10 times, which means that the performance of carbon-based chips is more than three generations ahead of that of silicon-based chips with the same technical node.

For example, carbon-based chips using 90 nm technology are expected to produce silicon-based chips with the same performance and integration level as 28 nm technology nodes; carbon-based chips using 28 nm technology can realize silicon-based chips equivalent to 7 nm technology nodes.

「 Our carbon-based semiconductor research represents the world's leading level. 」 Peng Lianmao said in an interview. Compared with chips manufactured by foreign silicon-based technologies, chips manufactured by carbon-based technologies in China not only process big data faster, but also save at least 30% of power consumption.

Three

Carbon nanotubes from American laboratory to industrial scenario

The continuous reduction of the size of silicon transistors promotes the progress of electronic technology. When Moore's law came to an end, it became more and more difficult for silicon transistors to shrink.

Transistor based on semiconductor carbon nanotubes, as a substitute for silicon transistor in advanced micro-electronic devices, is similar to metal oxide semiconductor field effect transistor (MOSFET), and becomes the basic unit for building the next generation of computers.

Of course, although carbon nanotube field effect transistors (CNFET) are more energy-saving than silicon field effect transistors, most of them still exist in laboratories. Now, the Shulaker research team of Massachusetts Institute of Technology optimizes the process of standard nano-tube deposition solution and deposits a small amount of nano-tube solution on the wafer, significantly improving the throughput, the speed of the deposition process is accelerated by more than 1,100 times, while the cost is reduced.

This enables them to manufacture carbon nanotube field effect transistors in commercial silicon manufacturing plants and large quantities of semiconductor OEM.

Max M. Shulaker is the first author of the first computer research results on carbon nanotubes in 2013; He joined MIT in 2016 as an assistant professor and continued to carry out research on carbon nanotubes.

At present, the core challenge of transferring carbon nanometre from laboratory to industrial scene is that all materials and processes used to manufacture carbon nanotube field effect transistors must meet the strict compatibility requirements of silicon-based commercial manufacturing facilities, the deeper challenge also lies in how to deposit carbon nanometers evenly on the industrial standard substrate size (wafer with a diameter of 200mm and above).

To realize this carbon nano-deposition technology, three conditions must be met:

One is to minimize the cost while ensuring large-scale production;

The second is to be able to use the existing equipment and not introduce prohibited chemical pollutants or particles;

The third is to achieve stronger performance than silicon base of the same size.

One of the most effective methods to construct CFNET in the laboratory is the nano-tube deposition method, that is, the wafer is immersed in the nano-tube liquid until the nano-tube sticks to the surface of the wafer.

The performance of carbon nanotube field effect transistors (CNFETs) is largely determined by the deposition process, which affects the number and direction of carbon nanotubes on the wafer surface. "They" either stick to the wafer in a random direction, or all are arranged in the same direction.

Although this deposition method is very practical for industry, it cannot align the nanotubes at all. Through careful observation of the deposition process, researchers found that dry circulation, a method of intermittently drying and soaking wafers, can greatly shorten the deposition time from 48 hours to 150 seconds.

A method for improving carbon nanotube deposition by ACE culture.

Therefore, they proposed ACE (artificial concentration by evaporation), which deposited a small amount of nano-tube solution on the wafer instead of soaking the wafer in the groove. Slow evaporation of the solution increases the concentration of carbon nanotubes and the overall density of the nanotubes deposited on the wafer.

At present, researchers have cooperated with Analog Devices of commercial silicon manufacturers and semiconductor foundry SkyWater Technology to manufacture CNFET using improved methods. They can use the same equipment used by the two factories to manufacture silicon-based wafers, and at the same time ensure that the nano-tube solution meets the strict requirements of the two factories for chemistry and pollutants.

It is worth noting that what the research produces is not a traditional computer chip, but only a demonstration of manufacturing process, and the gate length (I .e. process) of the transistor is 130nm, equivalent to the chip technology in the 2001 s. The new process also achieved only 45 nanotubes/Micron, which is still significantly lower than the optimal density of 200 previously predicted by researchers.

However, the researchers also analyzed the relationship between the density of nanotubes and energy efficiency: even at a lower density, the cost savings will be considerable. Even if the density of nanotubes is 25, it will bring about 2.5 times of energy efficiency improvement.

Although there is still a long way to go to transform this breakthrough into a practical chip technology, it is an important step towards the future of high-performance nanotube computing, it may become the next most important "weapon" after Moore's law 」.